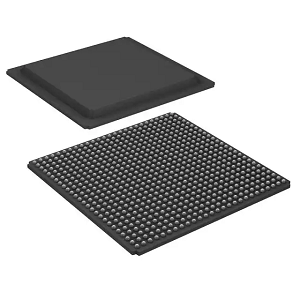

XC7Z030-2FFG676I – Integrerte kretser (IC), innebygd, system på brikke (SoC)

Produktegenskaper

| TYPE | BESKRIVELSE |

| Kategori | Integrerte kretser (IC) |

| Mfr | AMD |

| Serie | Zynq®-7000 |

| Pakke | Brett |

| Produktstatus | Aktiv |

| Arkitektur | MCU, FPGA |

| Kjerneprosessor | Dual ARM® Cortex®-A9 MPCore™ med CoreSight™ |

| Flash størrelse | - |

| RAM-størrelse | 256KB |

| Periferiutstyr | DMA |

| Tilkobling | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Hastighet | 800MHz |

| Primære attributter | Kintex™-7 FPGA, 125K logiske celler |

| Driftstemperatur | -40 °C ~ 100 °C (TJ) |

| Pakke / Etui | 676-BBGA, FCBGA |

| Leverandørenhetspakke | 676-FCBGA (27x27) |

| Antall I/O | 130 |

| Grunnproduktnummer | XC7Z030 |

Dokumenter og medier

| RESSURSTYPE | LINK |

| Dataark | Zynq-7000 Oversikt over alle programmerbare SoC |

| Produktopplæringsmoduler | Driver Series 7 Xilinx FPGAer med TI Power Management Solutions |

| Miljøinformasjon | Xiliinx RoHS-sertifisering |

| Utvalgt produkt | Alle programmerbare Zynq®-7000 SoC |

| PCN-design/spesifikasjon | Mult Dev Material Change 16/des/2019 |

| Errata | Zynq-7000 Errata |

Miljø- og eksportklassifiseringer

| EGENSKAP | BESKRIVELSE |

| RoHS-status | ROHS3-kompatibel |

| Moisture Sensitivity Level (MSL) | 4 (72 timer) |

| REACH-status | REACH Upåvirket |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Application Processor Unit (APU)

Nøkkelfunksjonene til APU inkluderer:

• Dual-core eller single-core ARM Cortex-A9 MPCores.Funksjoner knyttet til hver kjerne inkluderer:

• 2,5 DMIPS/MHz

• Driftsfrekvensområde:

- Z-7007S/Z-7012S/Z-7014S (trådbinding): Opptil 667 MHz (-1);766 MHz (-2)

- Z-7010/Z-7015/Z-7020 (trådbinding): Opptil 667 MHz (-1);766 MHz (-2);866 MHz (-3)

- Z-7030/Z-7035/Z-7045 (flip-chip): 667 MHz (-1);800 MHz (-2);1 GHz (-3)

- Z-7100 (flip-chip): 667 MHz (-1);800 MHz (-2)

• Evne til å operere i enkelt prosessor, symmetrisk dobbel prosessor og asymmetrisk dobbel prosessor modus

• Enkelt og dobbel presisjonsflytepunkt: opptil 2,0 MFLOPS/MHz hver

• NEON mediebehandlingsmotor for SIMD-støtte

• Thumb®-2-støtte for kodekomprimering

• Nivå 1 cacher (separate instruksjoner og data, 32 KB hver)

- 4-veis sett-assosiativ

- Ikke-blokkerende databuffer med støtte for opptil fire utestående lese- og skrivefeil hver

• Integrert minneadministrasjonsenhet (MMU)

• TrustZone® for drift i sikker modus

• Accelerator Coherency Port (ACP)-grensesnitt som muliggjør sammenhengende tilganger fra PL til CPU-minneplass

• Unified Level 2 cache (512 KB)

• 8-veis sett-assosiativ

• TrustZone aktivert for sikker drift

• Dual-ported, on-chip RAM (256 KB)

• Tilgjengelig med CPU og programmerbar logikk (PL)

• Designet for tilgang med lav ventetid fra CPU

• 8-kanals DMA

• Støtter flere overføringstyper: minne-til-minne, minne-til-perifert, perifert-til-minne og scatter-samler

• 64-bits AXI-grensesnitt, muliggjør DMA-overføringer med høy gjennomstrømming

• 4 kanaler dedikert til PL

• TrustZone aktivert for sikker drift

• Grensesnitt for doble registertilgang fremtvinger separasjon mellom sikker og ikke-sikker tilgang

• Avbrudd og timere

• Generell avbruddskontroller (GIC)

• Tre vakthundtimere (WDT) (en per CPU og en system-WDT)

• To trippeltimere/tellere (TTC)

• CoreSight feilsøkings- og sporingsstøtte for Cortex-A9

• Programmer sporingsmakrocelle (PTM) for instruksjon og sporing

• Cross trigger interface (CTI) som muliggjør hardware breakpoints og triggers